本文主要介绍说明XQ6657Z35-EVM 高速数据处理评估板SFP光口IBERT链路误码测试、使用步骤以及各个例程的运行效果。

(基于TI KeyStone架构C6000系列TMS320C6657双核C66x 定点/浮点DSP以及Xilinx Zynq-7000系列SoC处理器XC7Z035-2FFG676I设计的异构多核评估板,由核心板与评估底板组成。)

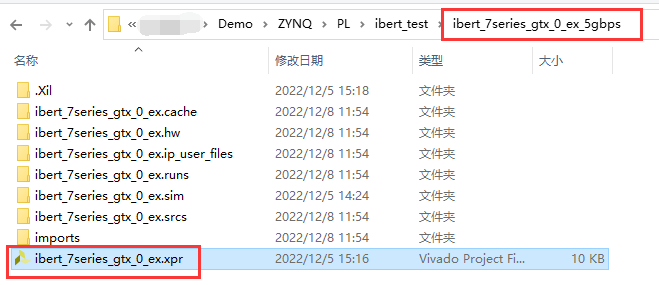

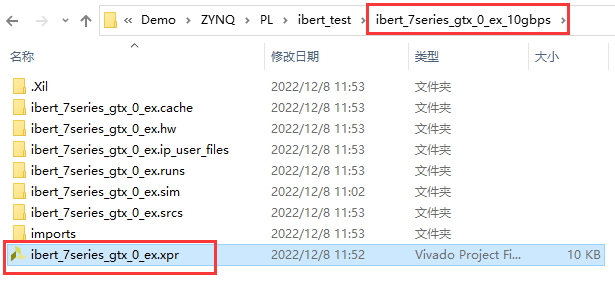

1.1 ZYNQ PL SFP光口IBERT链路误码测试1.1.1 例程位置ZYNQ IBERT链路误码测试例程有两个,分别用于光口运行在5Gbps和10Gbps两种线路速率情形下的误码统计和眼图测试,IBERT测试例程保存在资料盘中的位置如下:

(1)5Gbps IBERT例程存放位置:

Demo\ZYNQ\PL\ibert_test\ibert_7series_gtx_0_ex_5gbps文件夹下;

(2)10Gbps IBERT例程存放位置:

Demo\ZYNQ\PL\ibert_test\ibert_7series_gtx_0_ex_10gbps文件夹下。

1.1.2 功能简介LogiCORE IBERT IP核是Xilinx提供的集成式误码率测试IP核,该IP核产生测试样式,由发送端发出测试样式,经接收端接收测试样式并进行误码检测、分析,以检测Xilinx器件内部高速串行收发器的收发性能。由IBERT IP生成的测试工程会提供一个图形化测试界面,方便用户直观控制和检测高速串行收发器的参数指标。

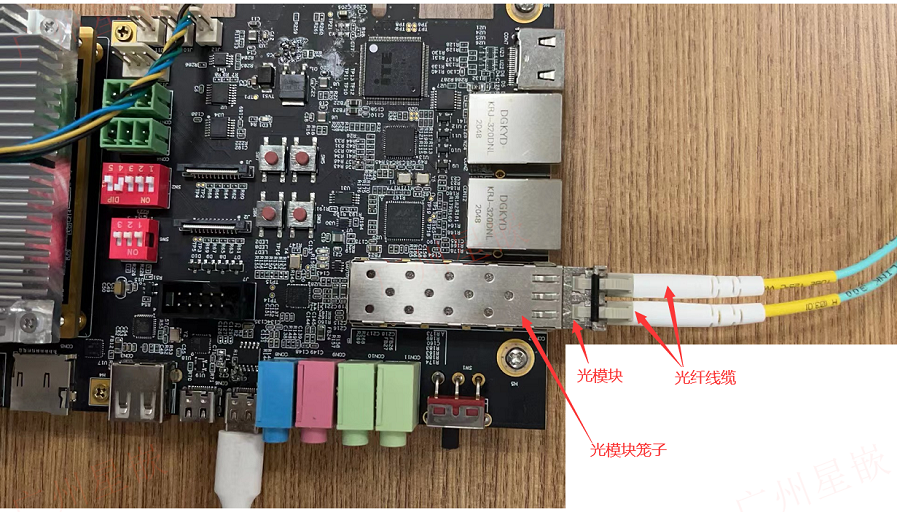

1.1.3 例程使用1.1.3.1 连接光纤模块将光模块插入光模块笼子,并使用光纤线缆将光模块的收、发端口自环对接:

打开Vivado示例工程,打开5Gbps IBERT例程或10Gbps IBERT例程:

或

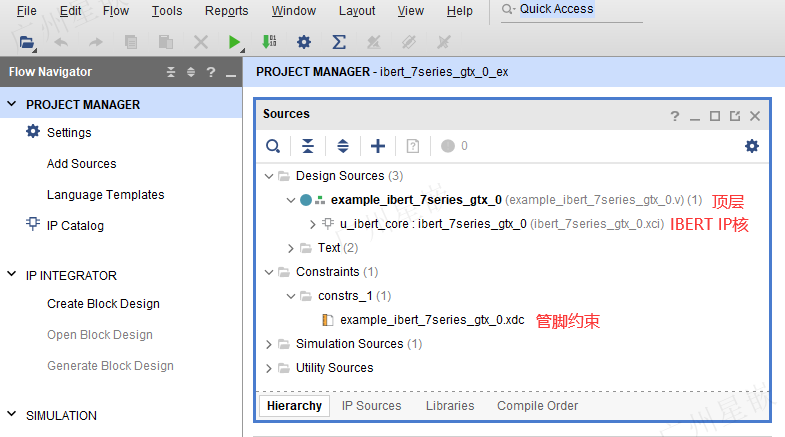

工程打开后界面及工程主要模块说明如下图所示:

1.1.3.2.2 下载ZYNQ PL程序

下载bit流文件example_ibert_7series_gtx_0.bit,如下图下载界面所示:

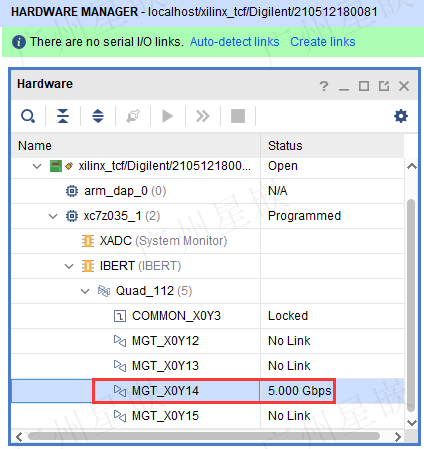

1.1.3.3 运行结果说明1.1.3.3.1 查看链路状态1.1.3.3.1.1 5Gbps速率测试时

可查看到MGT_X0Y14链路锁定在了5Gbps线路速率,通信链路已经建立起来:

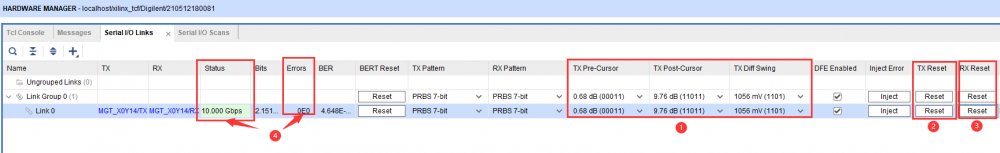

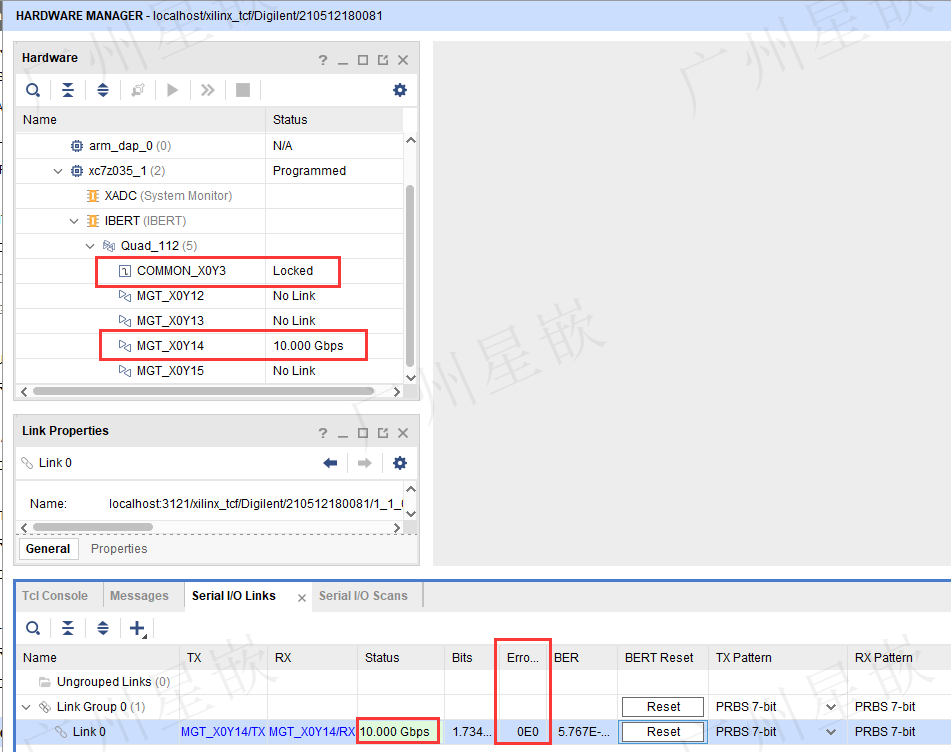

10Gbps速率测试时,需要用户根据板卡实际情况调节链路参数。在调试窗口的下方,有一个Serial I/O Links窗口,打开此窗口去完成链路参数调节任务。

用户调节Tx Pre-Cursor、 Tx Post-Cursor、Tx Diff Swing这三个链路参数,参数调节完毕后,首先点击TX Reset,然后点击RX Reset,最后再查看Status和Errors状态,直到Status显示出预期的线路运行速率,比如10Gbps,且Errors=0E0,即误码,则表示链路目前运行正常:

1.1.3.3.2 查看眼图

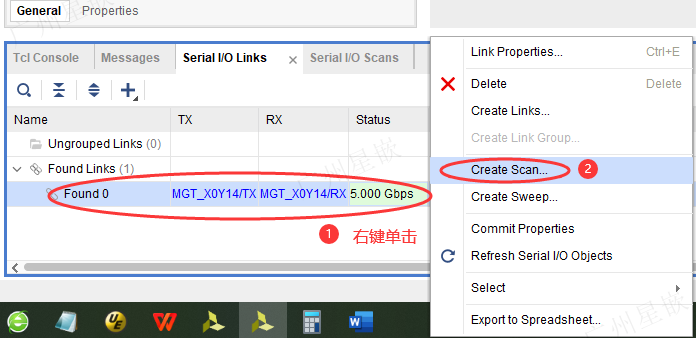

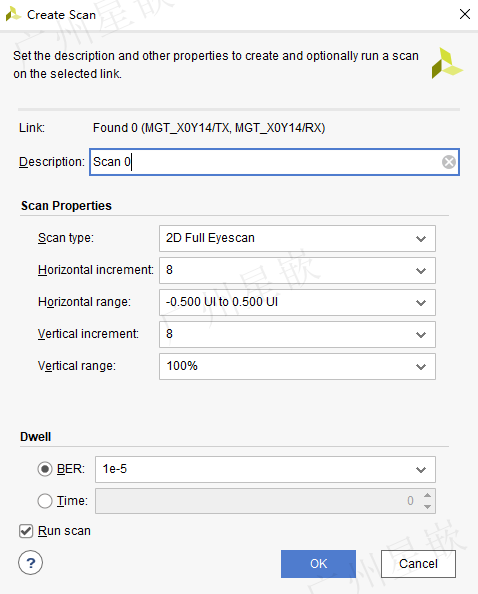

在Serial I/O Scans窗口,点击创建链路,然后再针对链路创建眼图扫描:

设置眼图扫描参数:

1.1.3.3.2.1 眼图测试结果

1.1.3.3.2.1.1 5Gbps速率测试时

1.1.3.3.2.1.2 10Gbps速率测试时

1.1.3.4 退出实验

Vivado调试界面Hardware Manager窗口,右键单击localhost(1),在弹出的菜单中点击Close Server,断开ZYNQ JTAG仿真器与板卡的连接。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。